System-Level Test Essential for Fast-Growing Embedded NAND Market

By Ken Hanh Duc Lai, Marketing Director, Advantest America

The market for NAND flash memories is growing at a rapid pace, driven in large part by the massive demand for solid state drives (SSDs), which have replaced hard disk drives for many applications. According to Gartner, the SSD market will reach above 370 million units in 2020, and IC Insights forecasts that memory IC products will show the strongest growth rate through 2021 of the four major IC product categories (the others being logic, analog and microcomponents).

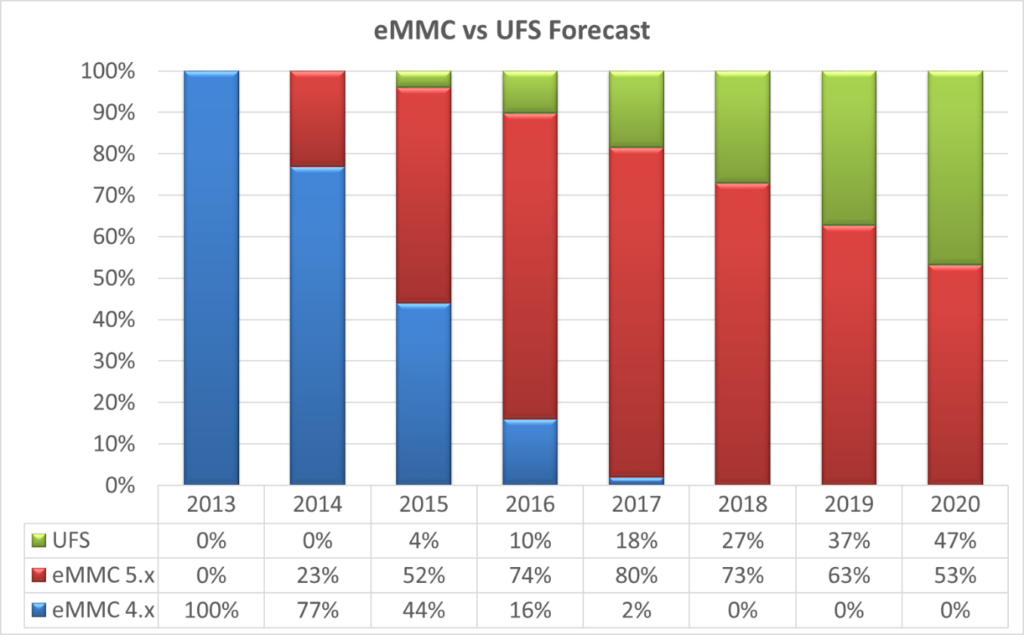

A significant portion of the SSD market is commanded by PC servers and clients used for big data storage applications. However, the mobile market comprising portable wireless devices like smartphones and tablet PCs is growing as well, with variations in form factor increasing to meet new market demands. Driven by these applications, mobile memory unit shipments are forecast to exceed 2 billion units by 2020. These include embedded multimedia cards (eMMC), embedded multi-chip packages (eMCP), MCP and raw NAND. In concert with this growth, the embedded NAND market is undergoing a shift in protocol usage. Embedded NAND is in 80 percent of the smartphones currently on the market, and while smartphones and tablets have typically used eMMCs to store information, a transition is under way from eMMC to Universal Flash Storage (UFS) as the future of flash memory (see Figure 1).

Figure 1. UFS has taken hold, and is expected to represent half the market for NAND flash SSDs by 2020. (Source: IHS Mobile and Embedded Memory Market Tracker Q4 2016)

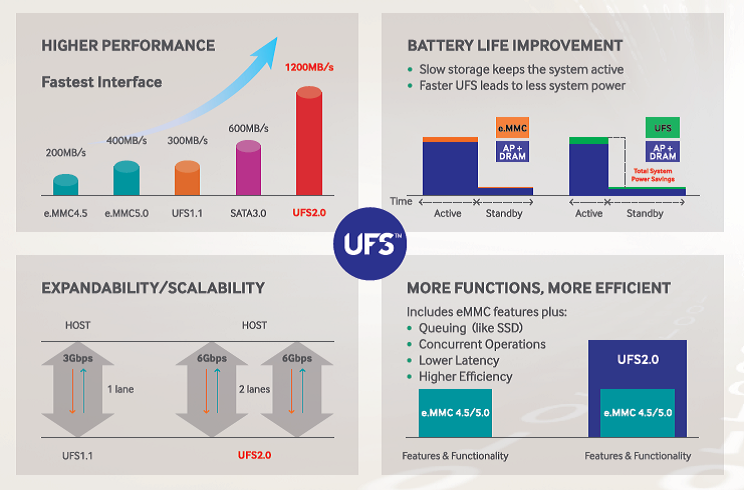

The JEDEC-defined UFS mobile-centric storage standard addresses next-generation mobile performance and scalability, offering fast sequential read/write speeds with high random IOPS1, which are essential for mobile phones. (For SSDs, random IOPS numbers are primarily dependent upon the storage device’s internal controller and memory interface speeds.) One key value of UFS is its ability to leverage the strengths of several existing technologies in one standard: the low power consumption of eMMC; the MIPI interface standard, M-PHY and UniPro, for the interconnect layer; and the SCSI command set as the application protocol.

Devices based on UFS 2.0, the current version of the standard, offer the highest available performance of any SSD interface standard due to its separately dedicated read/write paths, which enable UFS to read and write simultaneously. At up to 1200 Megabytes per second (MB/s), UFS operates at twice the rate of Serial ATA (SATA) 3.0 and three times that of eMMC5.0. UFS also consumes less total power by processing tasks sooner and staying in standby mode longer. Figure 2 summarizes the key benefits of UFS standard.

Figure 2. UFS offers a number of benefits that make it a superior option for embedded storage in mobile devices. (Source: Universal Flash Storage Association)

UFS is here

Adoption of UFS in the U.S. has already begun, with most of the top 10 mobile handset OEMs using UFS memory for their flagship models. While this includes primarily high-end handsets at the moment, as the cost to implement UFS continues to decline, more and more mid-tier phones will incorporate UFS-based embedded NAND memory devices. Moreover, the ecosystem for UFS is already in place, with a range of vendors supporting the UFS interface, including makers of NAND flash, systems-on-chip (SoCs), operating systems, measurement tools, and testers optimized for high-volume manufacturing (HVM).

Major NAND makers and manufacturers of UFS and BGA2 SSDs have adopted system-level test (SLT) for production use. More than 50 testers overall have been installed since the second half of 2016 for system-level testing of UFS and BGA SSDs, and this number is expected to triple during 2017.

Flexible tester optimized for embedded NAND

Memory IC makers need a class of tester that specializes in SLT of these devices, while maintaining the reliability, low cost and high volume capabilities required for conventional memory testers. Advantest developed its T5851 system-level test (SLT) solution – part of the T5800 platform series – specifically to meet these needs, delivering cost-effective testing of UFS and BGA SSDs. Built with the same proven test architecture used in Advantest’s MPT3000 family of SSD protocol test solutions, the T5851 allows customers to minimize both their capital investments and deployment risks by using the same platform and FutureSuite™ software as other members of the T5800 product line.

The flexible T5851 tester is available in both production and engineering models, allowing the system to be used for reliability and qualification testing as well as test-program development or, when equipped with an automated component handler such as Advantest’s M6242, high-volume production. As a fully integrated SLT solution, the T5851 provides multi-protocol support in one tool while its tester-per-DUT [device under test] architecture and proprietary hardware accelerator allow it to achieve industry-leading test times.

Currently, Advantest has many T5851 systems installed at IDM3 and OSAT4 customer sites worldwide for HVM production, qualification and engineering. This number is expected to increase as adoption of UFS becomes more widespread. This will be spurred by the release of UFS 3.0, as well as expansion of the standard into other applications, such as memory cards, PC clients, smart TVs, and automotive devices, which are anticipated to be the next emerging market for UFS. Advantest, as always, is working with its customers to stay on top of these developments to ensure its testers are future-ready to accommodate new requirements as they arise.

Notes:

IOPS = input/output operations per second

BGA = ball grid array

IDM = integrated device manufacturer

OSAT = outsourced semiconductor assembly and test

Q&A Interviewee

Q&A Interviewee

As VOICE enters its second decade in 2017, the conference will continue to offer attendees comprehensive learning and networking opportunities including technical presentations focused on eight technology tracks, partners’ expositions and social gatherings. In addition, the VOICE Technology Kiosk Showcase will expand to include more interactive discussion sessions for users of Advantest’s V93000 and T2000 system-on-a-chip (SoC) test platforms, memory test systems, handlers, test cell solutions, product engineering and test technology.

As VOICE enters its second decade in 2017, the conference will continue to offer attendees comprehensive learning and networking opportunities including technical presentations focused on eight technology tracks, partners’ expositions and social gatherings. In addition, the VOICE Technology Kiosk Showcase will expand to include more interactive discussion sessions for users of Advantest’s V93000 and T2000 system-on-a-chip (SoC) test platforms, memory test systems, handlers, test cell solutions, product engineering and test technology. Device-Specific Testing

Device-Specific Testing Test Methodologies

Test Methodologies