Data Collection and Analysis Drives Semiconductor Test in the Era of Chip Convergence

This article is a condensed version of an article published February 16, 2022, on JIWEI Net. Adapted with permission. Read the original article at https://www.laoyaoba.com/html/share/news?source=app_android_v2&news_id=806699&sign=5ab5d193a7e37db4e4b7728f73e6a208

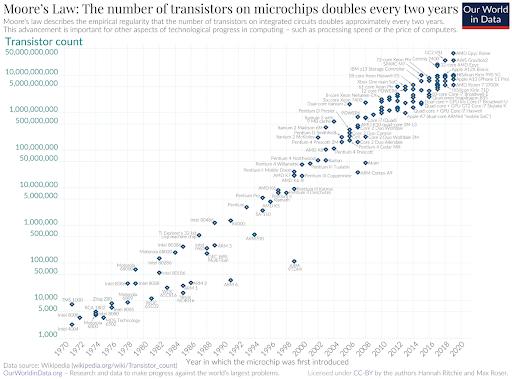

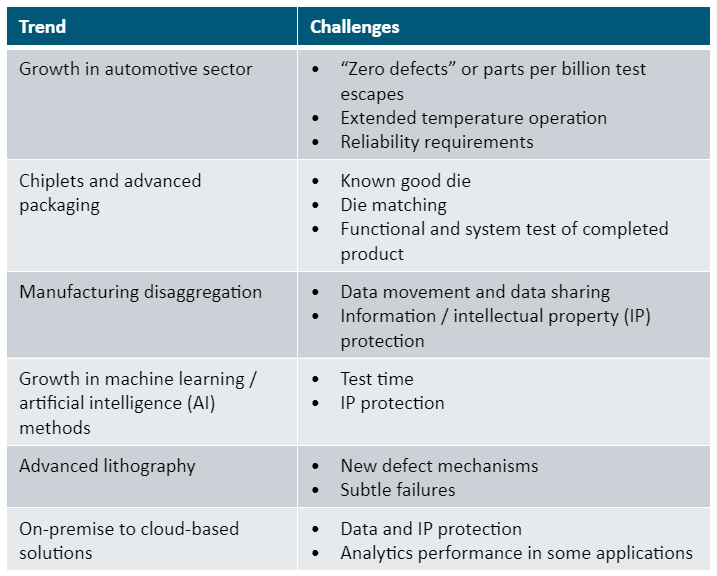

In the Age of Convergence, many forces are driving continuous advancement of semiconductor testing technology. As more and more functions are carried on a chip, and technology grows more and more complex, the number and types of test steps must be multiplied – leading, in turn, to increased test costs. Semiconductor test equipment requires ultra-long “standby,” which is an asset-heavy investment in semiconductor manufacturing plants, with a life cycle of at least 5 to 10 years. In an intelligent world where chip technology and processes are rapidly upgraded and iterated, such equipment must be able to meet increasingly complex testing needs at any time.

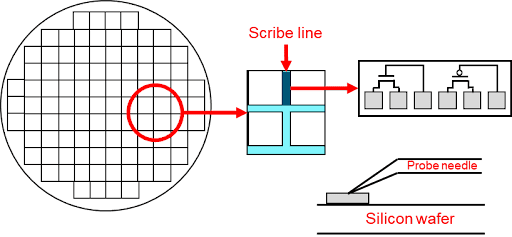

As a result, test and measurement solutions must expand to address the entire semiconductor industry value chain. This includes not only the traditional “center” of testing (IC production processes, wafer test and final test), but also greater integration with IC design and more system-level testing (SLT) at the product level, plus connectivity, including the cloud, artificial intelligence (AI) and Big Data.

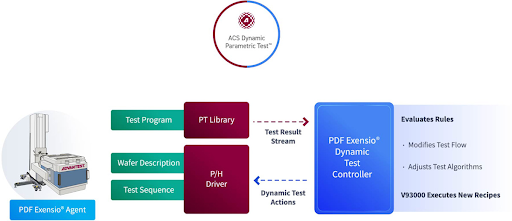

Advantest and PDF Solutions’ collaboration [first announced in July 2020], targets these expanded capabilities. By combining PDF Solutions’ Exensio platform and its Data Exchange Network (DEX) with Advantest’s advanced test equipment (ATE), customers can connect and analyze data anywhere in the semiconductor supply chain, helping them improve product yield and reduce test costs.

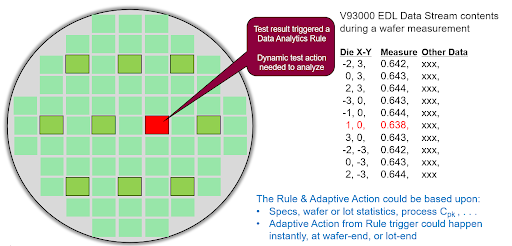

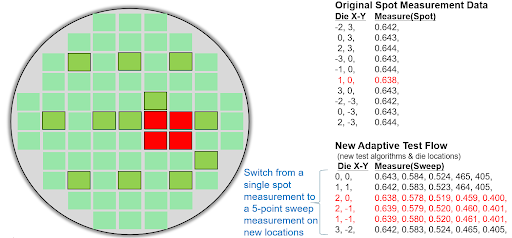

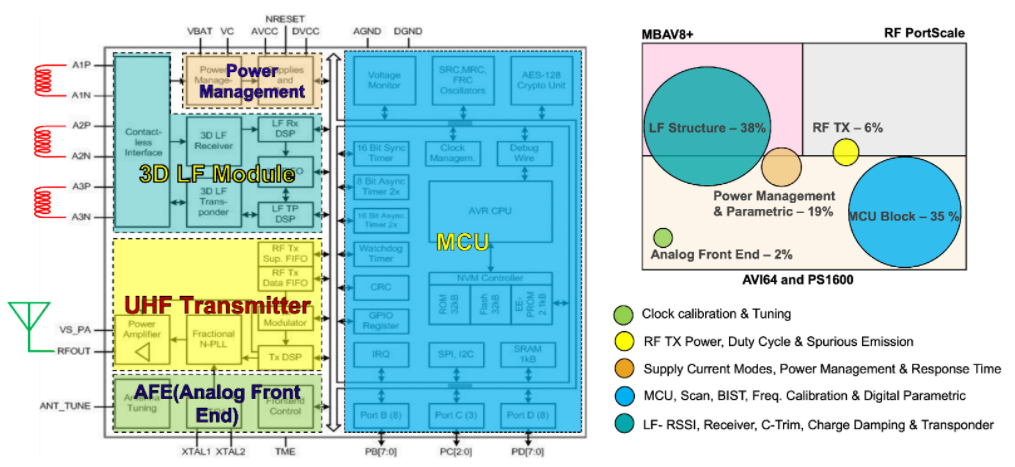

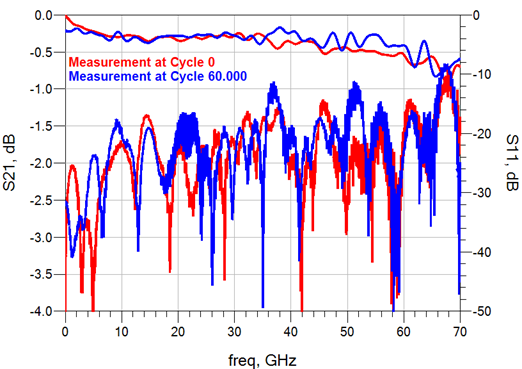

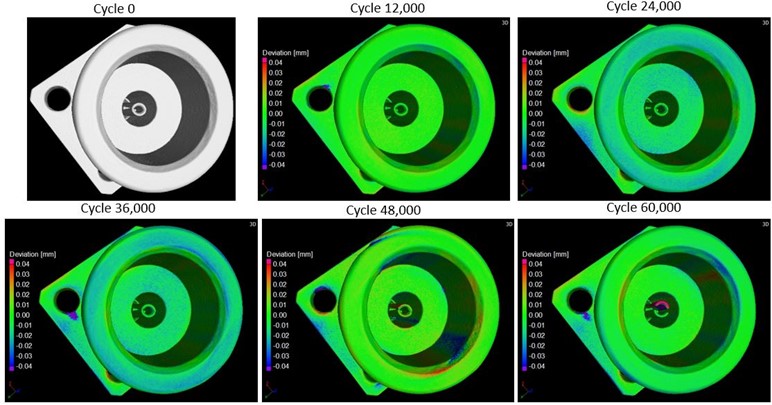

The two companies’ jointly developed product – ACS Dynamic Parametric Test (DPT) – integrates PDF Solutions’ Exensio data analysis products with Advantest’s V93000 parametric test system, enabling real-time optimization of parametric tests on the V93000 test platform and reducing manual interaction. The figure below illustrates the ACS DPT solution elements and functionality.

The balance of the article comprises an interview (also excerpted) with executives from both companies: Advantest’s Keith Schaub, vice president of strategy and technology, and Sonny Banwari, ACS vice president of business development; and PDF Solutions’ Guanyuan (Michael Yu), vice president of sales and operations, and David Park, vice president of marketing.

What are the key benefits of the Advantest-PDF collaboration, and why are they important for the semiconductor industry?

Keith: Advantest has a long history in semiconductor testing, and we are the market leader in high volume manufacturing of semiconductor test products, with a range that spans from post-silicon validation, all the way to system-level test. Now, there is a lot of big data coming out of the test eco-system, and the industry has realized the future is using tools like AI and machine learning to mine data value, to improve the operational efficiency of the entire ecosystem, and of the entire supply chain.PDF Solutions is well established and strong in data analytics, and an ideal partner for bringing this advanced technology to the fore.

Michael: Advantest is the world’s leading supplier of semiconductor test equipment. Over the decades, it has amassed an enormous amount of knowledge and data related to semiconductor testing. PDF has always focused on data analysis of the entire semiconductor industry chain. The key point of this cooperation is to interconnect test-related data with the entire industry chain. For example, some data before testing, such as manufacturing-related data, can help to decide which devices to test and how to improve testing efficiency and quality. At the same time, data from these test cells can be brought forward to the subsequent steps of the supply chain and can also be fed back to obtain a more reliable and efficient test plan.

While the semiconductor industry is data-intensive, it is relatively backward in data analysis. What are the major obstacles? How will your joint data analytics-based products impact the industry?

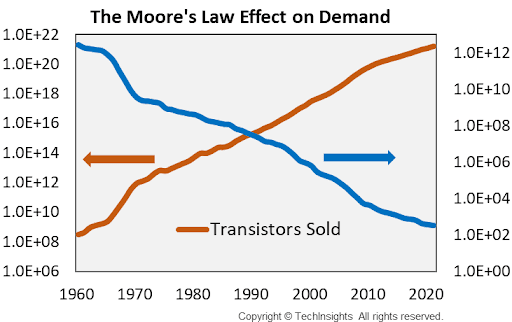

Keith: The global semiconductor industry is in a period of rapid growth, and the huge market size brings huge growth opportunity for companies throughout the entire industry supply chain. At the same time, end-user applications are increasingly diverse and complex, with higher requirements for the quality and reliability of electronic components such as IC chips. Making test scheme coverage more comprehensive increases test cost. How do we control the cost of testing under the premise of ensuring higher quality? By mining the value of semiconductor data.

ACS powered by PDF Exensio is equivalent to providing the industry with an infrastructure platform for data analysis of the entire semiconductor supply chain. PDF Exensio can help collect data from semiconductor chip fabrication, test, and system-level test. With advanced algorithms, integrated workflows, and solutions delivered by ACS, more valuable information can be gained from the data generated by supply chain equipment and testing, resulting in shorter production times and higher overall equipment efficiency.

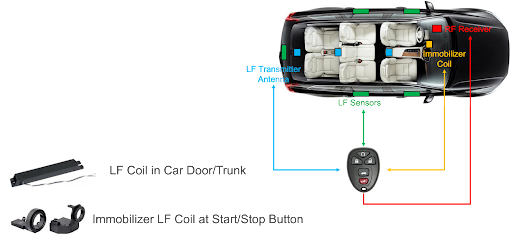

Sonny: As an example, the global chip shortage is a crisis for all industries, especially the automotive industry. In fact, this crisis has further forced carmakers to optimize products and technologies to deal with the chip shortage. The cooperation between Advantest and PDF Solutions is doing a similar thing: improving product yield through data analysis and providing customers with better products. It’s just reducing a company’s costs and improving its profitability, but it’s giving an opportunity for the entire semiconductor ecosystem to upgrade.

Michael: Indeed, to ensure the quality and reliability of chips, especially automotive chips, you need extensive testing, and that takes tremendous time and effort. But if we can adopt a traceable system and integrate the data of the entire production process, we can use AI and machine learning to tell us what to test, and what’s the most efficient way to perform the test. Instead of just one size fits all, with data analysis obtained through AI and machine learning, we can carry out personalized test plans for different quality requirements and find the best test results in the shortest time.

David: About five years ago, people were hesitant about going to cloud, mainly due to concerns about data security and privacy, especially in the semiconductor industry. This is the biggest obstacle for data analysis in the semiconductor industry. How to get enterprises across the supply chain willing to share data is a key step, and this is one aspect of what we are trying to do, to create a safe data sharing ecosystem. For example, both Advantest and PDF are involved in an initiative out of the GSA (Global Semiconductor Alliance) called TIES (Trusted IOT Ecosystem for Security), with the goal to bring together all the different players in the semiconductor supply chain, from design to manufacturing, packaging, and testing, to jointly form a secure trusted data sharing ecosystem.

Working remotely has also greatly promoted investments in cloud infrastructure, and the semiconductor industry is now a bit more open to moving data to the cloud. Being in the cloud will bring a more efficient and convenient data ecosystem to the entire semiconductor supply chain, for both scalability and computing performance.

In terms of empowering the semiconductor industry with intelligent means, such as big data analysis, cloud, and AI, what are the new trends in the future?

Keith: For a long time, the industry tended to use a one-size-fits-all general test solution, but different applications require customized test scenarios. However, with the increasing complexity of semiconductor process technology and the diversity of application requirements, the quality requirements for chips and other electronic components will also be different. Moreover, in the current environment of supply chain shortages, optimizing the test plan with different quality requirements for devices and use the big data analytics to control the test cost is vital. This is also what we are doing in cooperation with PDF Solutions.

Sonny: In the future, we will also increasingly tap the potential of AI-based and machine learning to develop more killer applications. Advantest and PDF understand each other, and we look forward to working together to elevate the power of machine learning to a new level in semiconductor testing and data analysis.

Michael: As technology progresses, the manufacturing process becomes more and more complex; in addition, as chip size increases, there are more and more functions, which means that the amount of testing will also increase, and the whole process will generate an increased amount of data. And how to effectively leverage all of this data – through machine learning, AI, cloud computing and other methods, including data mining, to improve the overall efficiency of semiconductor manufacturing and optimize costs – will become more and more important.

Read More